# Double side interconnection for vertical power components based on macro and nano structured copper interfaces and printed circuit board technologies

7<sup>th</sup> Micro/Nano-Electronics Packaging and Assembly, Design and Manufacturing Forum May 22-23 2019 – WTC GRENOBLE France

> <u>Bojan DJURIC<sup>12</sup></u>, Vincent BLEY<sup>2</sup>, Julien MORAND<sup>1</sup>, Olivier DAGUT<sup>2</sup>, Jean-Pascal CAMBRONNE<sup>2</sup>, Stefan MOLLOV<sup>1</sup>

<sup>1</sup>Mitsubishi Electric R&D Centre Europe 1, allée de Beaulieu CS 10806 35 708 RENNES CEDEX 7 France <sup>2</sup>Université de Toulouse; UPS; INPT; LAPLACE; 118 rte de Narbonne – Bât. 3R3 CNRS; LAPLACE; F-31062 Toulouse France

Context

Manufacturing process

**Experimental results**

Conclusion

MiNaPAD Forum 2019

Laplace

2

# INTRODUCTION

### Stronger power ratings ensured by

- 1. Interleaved topologies : Multicellular structures

- Reducing of passive components size

- Active components multiplying

- 2. Switches improvement : Wide band gap materials

- Increasing of switching frequency

- Higher working temperature

Active switches integration is sought

- 1. Reduce stray elements (and size)

- 2. Enhancement of thermal management (reliability)

Figure 1: 3.3 kW ac/dc converter with SiC power devices

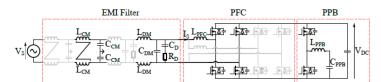

# INTRODUCTION

### **Motivation**

Figure 2: Zoom on parasitic elements (red) of the high side switching cell induced by the packaging

2. Capable of handling many thermal cycling

before failure

Introduction

# Context

Manufacturing process

**Experimental results**

Conclusion

MiNaPAD Forum 2019

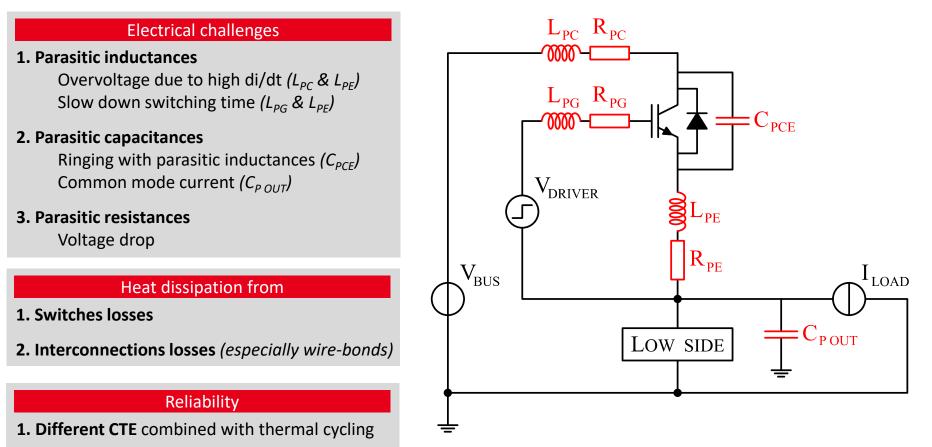

### Interconnection state-of-the-art

# Printed Circuit Board (PCB)

### Printed Circuit Board (PCB) technology is

- Cost efficient and well-established process

- Offering massive parallel manufacturing

- Capable of fine pitch and able to use thick copper (heat and current transport)

- Accurate repeatable multilayer structures

- Fan-out capable

- Minimizing of loop size (stray inductances)

### **PCB-embedding offers**

- 1. Double sided thermal dissipation and shorter heat path

- 2. Short interconnections and low parasitics

- 3. Increasing power density (by size reducing)

#### Laser micro vias

6

- Is the trend in PCB embedding interconnection

- Suffer of heat flux limitations (manufacturing limits)

Full µVias interconnections

diffusion bonding and  $\mu \text{Vias}$  interconnections

Soldering and foam interconnections

Galvanic Cu and vias interconnections

μVias and sintering interconnections

MiNaPAD Forum 2019

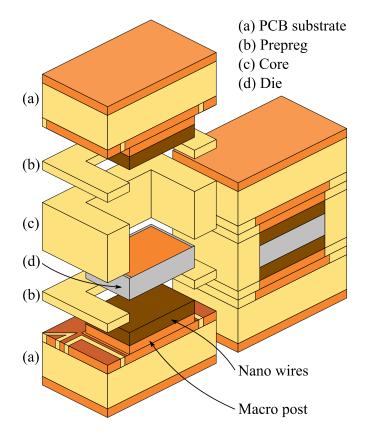

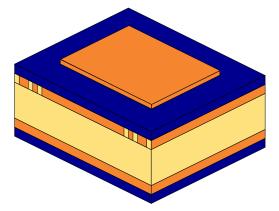

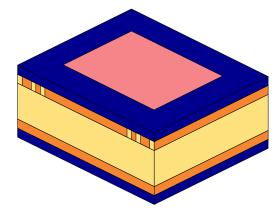

# CONTEXT

### Assembly

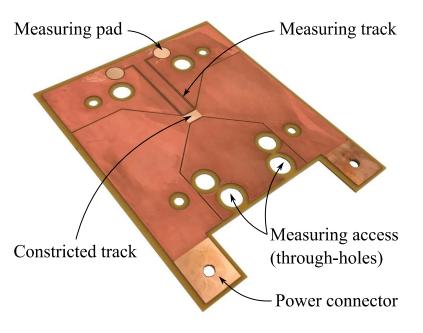

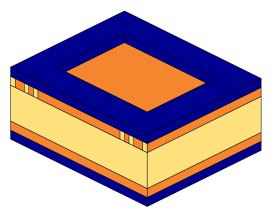

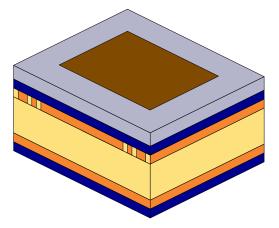

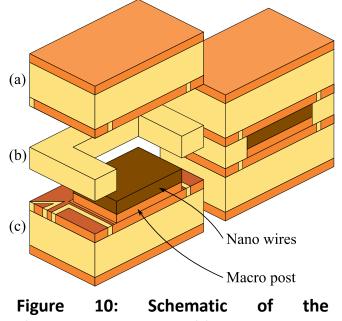

#### **Proposed solution combines**

- PCB substrates (a)

- having a macro post and nano wires interconnection

- sandwiching a die (d) surrounded of core (c)

- assembled by thermo-compression of prepregs (b)

### High level of integration

- Double-side cooling possible (symmetrical structure)

- 2. Full copper and flexible interconnection

- 3. Expected resistant to cyclical stresses

- 4. Elementary block for power converter

Figure 3: Cross section schematic of the assembly with macro and nano structured interfaces

Introduction

Context

# Manufacturing process

**Experimental results**

Conclusion

MiNaPAD Forum 2019

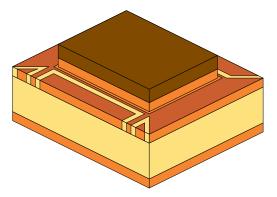

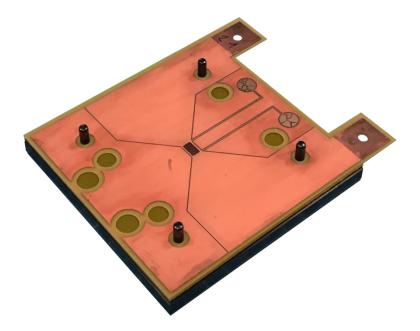

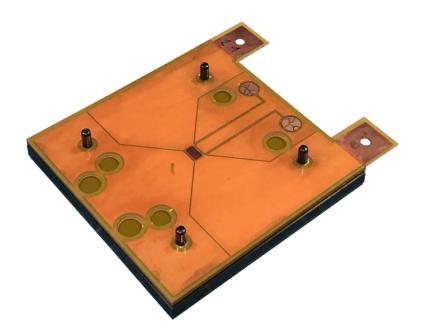

## **PCB** substrate functions

A 0.8 mm high temperature core with two 105  $\mu m$  thick copper layers

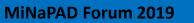

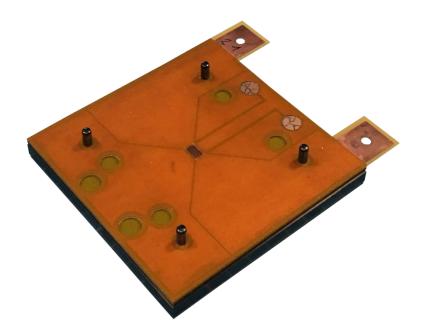

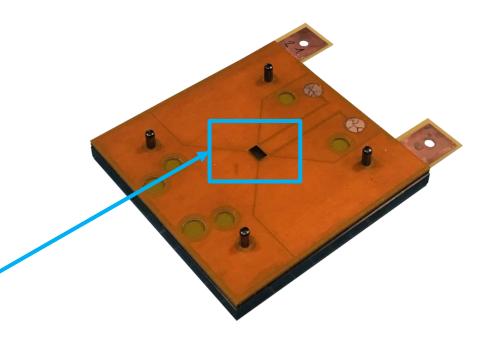

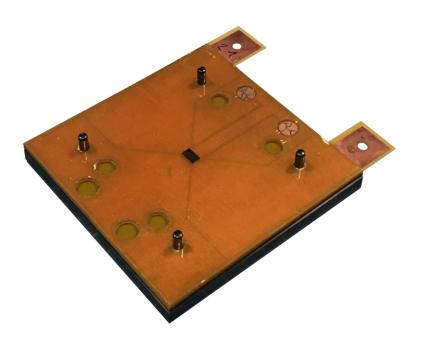

Figure 4: PCB substrate with constricted area, its connectors and kelvin measuring tracks

#### **Power connectors**

For electrical and thermal characterization

### **Constricted** area

- Bare copper area for the interconnection manufacturing

- Constriction is done for helping thermal characterization

#### Measuring pads and tracks

Additional contacts for Kelvin measurements

#### **Measuring accesses**

To the opposite substrate measuring pads

### Brown oxidized remainder copper and ground planes to increase prepreg adhesion

### Interconnection

#### > Opened dry film on constricted area

- a. Dry film deposition (≈ 45 µm) on the whole PCB surface;

- b. Opening of the dry film over the constricted area.

Figure 5: Manufacturing process of interconnection on the PCB substrate

### Interconnection

Opened dry film on constricted area

- Copper electro-etching on the constriction

- a.  $\approx$  7 µm copper electro-etching (pulsed waveform) to increase adhesion of the surface.

Figure 5: Manufacturing process of interconnection on the PCB substrate

### Interconnection

Opened dry film on constricted area Copper electro-etching on the constriction

- Macro post electroplating (overflowing of dry film)

- a. ≈ 60 µm copper electroplating (pulsed waveform) The electroplating profile is adjusted to have the top of the post slightly higher than the dry film to ensure a complete filling of the cavity.

Figure 5: Manufacturing process of interconnection on the PCB substrate

Opened dry film on constricted area Copper electro-etching on the constriction Macro post electroplating (overflowing of dry film)

### Leveling of the macro post by electro-etching

a. ≈ 7 µm copper electro-etching (pulsed waveform) The copper post is etched to obtain a flushed surface between the dry film and the copper post. This is the condition to ensure a correct sealing for the forthcoming steps.

Figure 5: Manufacturing process of interconnection on the PCB substrate

Laplace

### Interconnection

Opened dry film on constricted area Copper electro-etching on the constriction Macro post electroplating (overflowing of dry film) Leveling of the macro post by electro-etching

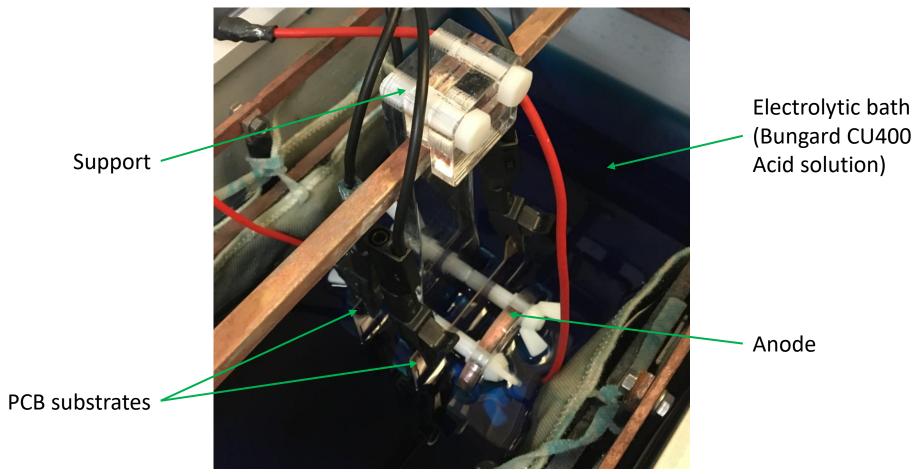

### > Nano wires electroplating by pressed anode

- a. A nanoporous membrane is placed on top of the copper post;

- b. A solution of copper sulfate is spread over to act as an initiator;

- c. 2 layers of cellulosic papers are added on top as solution buffer;

- d. A copper anode is pressed on top of this assembly;

- e. Copper is electroplated during ≈ 1 hour through the membrane using a pulsed waveform.

Figure 5: Manufacturing process of interconnection on the PCB substrate

### Interconnection

Opened dry film on constricted area Copper electro-etching on the constriction Macro post electroplating (overflowing of dry film) Leveling of the macro post by electro-etching Nano wires electroplating by pressed anode

### Membrane filling by distanced anode

Once the electrodeposition have been initiated

- a. The 2 layers of cellulosic papers are removed;

- b. The anode is placed further away;

- c. ≈ 6 hours copper electroplating is done until the membrane is filled.

Figure 5: Manufacturing process of interconnection on the PCB substrate

### Interconnection

Opened dry film on constricted area Copper electro-etching on the constriction Macro post electroplating (overflowing of dry film) Leveling of the macro post by electro-etching Nano wires electroplating by pressed anode Membrane filling by distanced anode

- Dry film and membrane removal

- a. Sodium hydroxide treatment at 45°C during half an hour.

Figure 5: Manufacturing process of interconnection on the PCB substrate

#### Interconnection

Figure 6: Nano wires electroplating on 2 parallel substrates with Bungard COMPACT A equipment

MiNaPAD Forum 2019

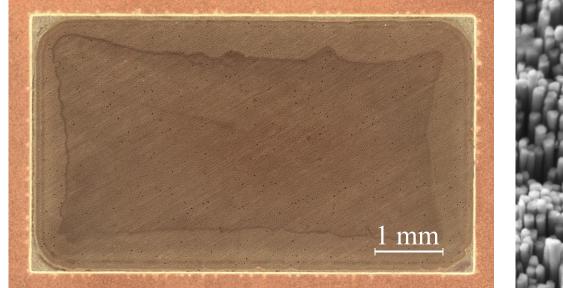

### Interconnection

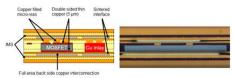

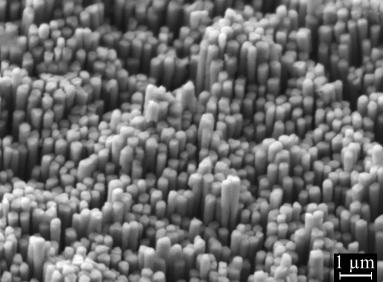

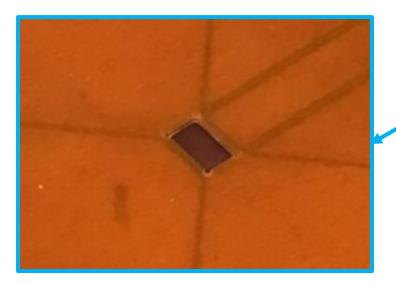

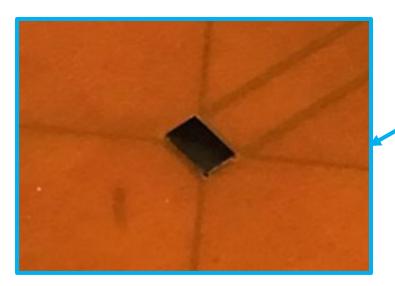

Full copper interconnection : 45  $\mu$ m macro post and 55  $\mu$ m nano wires of 200 nm diameter

Figure 7: Digital microscope picture (x200) of the macro and nano structured interface

Figure 8: SEM acquisition (x10,000) of the nano wires 40° tilted top view

- Consistent and continuous = good heat and current transport

- Nano wires well separated = flexible stress resistant interface

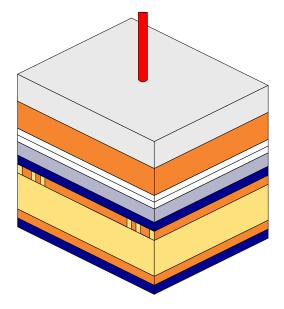

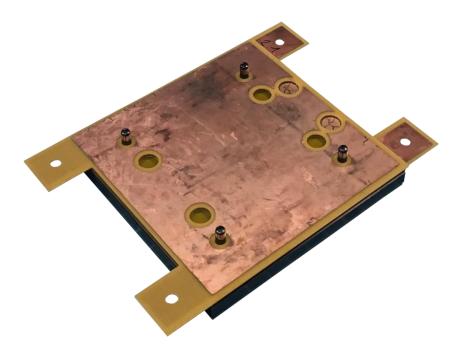

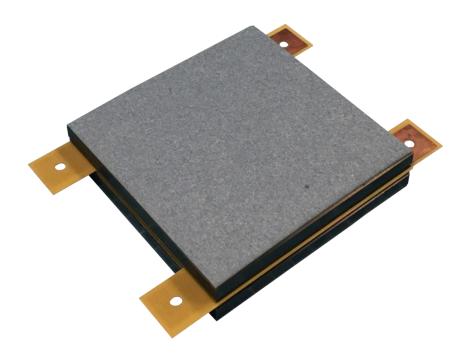

## **Test vehicles assembly**

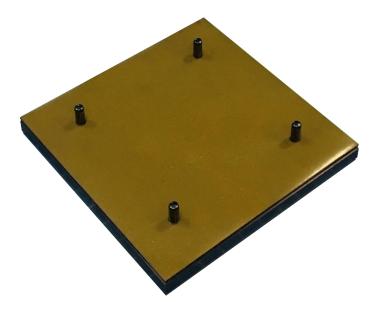

### Preparation of the support

- a. Bottom plate;

- b. 4 centering pins;

- c. 1st release film;

- d. Conformable press pad;

- e. 2nd release film.

### **Test vehicles assembly**

Preparation of the support

- Macro-nano structured PCB substrate

- a. Deoxidized by 10% sulfuric acid treatment;

- b. 12 hours annealing at 120°C.

### **Test vehicles assembly**

Preparation of the support Macro-nano structured PCB substrate

- Prepreg Arlon 35N 106

- a. Laser cut-out.

### **Test vehicles assembly**

Preparation of the support Macro-nano structured PCB substrate Prepreg Arlon 35N 106

### Core Arlon 35N

- a. Stratification of prepregs Arlon 35N (1 × 2116, 1 × 1080 and 2 × 106);

- b. Through holes and routing by CNC device.

### **Test vehicles assembly**

Preparation of the support Macro-nano structured PCB substrate Prepreg Arlon 35N 106

Core Arlon 35N

Figure 9: Stacking of the different elements of the prototype

MiNaPAD Forum 2019

### **Test vehicles assembly**

Preparation of the support Macro-nano structured PCB substrate Prepreg Arlon 35N 106 Core Arlon 35N

#### ➢ Bare die

### **Test vehicles assembly**

Preparation of the support Macro-nano structured PCB substrate Prepreg Arlon 35N 106 Core Arlon 35N Bare die

- Prepreg Arlon 35N 106

- a. Laser cut-out.

### **Test vehicles assembly**

Preparation of the support Macro-nano structured PCB substrate Prepreg Arlon 35N 106 Core Arlon 35N Bare die Prepreg Arlon 35N 106

#### Macro-nano structured PCB substrate

- a. Deoxidized by 10% sulfuric acid treatment;

- b. 12 hours annealing at 120°C.

### **Test vehicles assembly**

Preparation of the support Macro-nano structured PCB substrate Prepreg Arlon 35N 106 Core Arlon 35N Bare die Prepreg Arlon 35N 106 Macro-nano structured PCB substrate

### Closing of the support

- a. Implementation of the release films and the press pad and therefore the top plate;

- b. 1 hour under vacuum;

- c. Protective layers on both sides.

### **Test vehicles assembly**

Preparation of the support Macro-nano structured PCB substrate Prepreg Arlon 35N 106 Core Arlon 35N Bare die Prepreg Arlon 35N 106 Macro-nano structured PCB substrate Closing of the support

### Pressing of the prototype

- a. Pressing with Arlon 35N recommended profile;

- b. Removing of the assembly from the support.

### **Test vehicles assembly**

Preparation of the support Macro-nano structured PCB substrate Prepreg Arlon 35N 106 Core Arlon 35N Bare die Prepreg Arlon 35N 106 Macro-nano structured PCB substrate Closing of the support Pressing of the prototype

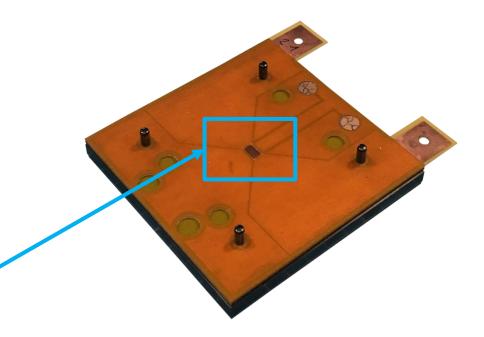

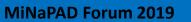

### Caption

- a. Measuring pads of (A) bottom and (B) top substrate;

- b. Power connectors of (C) top and (D) bottom substrate.

Figure 9: Stacking of the different elements of the prototype

MiNaPAD Forum 2019

Introduction

Context

Manufacturing process

**Experimental results**

Conclusion

MiNaPAD Forum 2019

# **EXPERIMENTAL RESULTS**

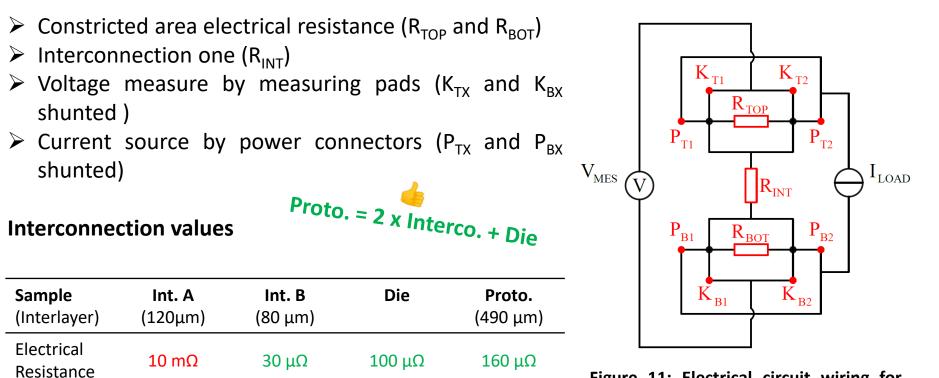

### **Electrical characterization**

#### Interconnection assembly

- Bare PCB substrate (a)

- Assembled by thermo-compression of a prepreg (b)

- ➤ To macro-nano structured (≈ 100 µm) PCB substrate (c)

#### Characterization

Two assemblies with different prepreg (interlayer)

- > A 120  $\mu$ m layer of prepreg (study case A)

- A 80 μm layer of prepreg (study case B)

characterization assembly

# **EXPERIMENTAL RESULTS**

### **Electrical characterization**

#### **Kelvin measurement**

Figure 11: Electrical circuit wiring for interconnection kelvin measurement

<u>NB:</u> Table's +/- 5% rounded measurements taken at room temperature

life.augmented

# EXPERIMENTAL RESULTS

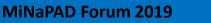

### **Electro-thermal characterization**

#### Evaluating of thermal resistance (R<sub>th</sub>) by

- 1. Controlling power flux on one side (P)

- 2. Measuring applied heat on the other ( $\Delta T$ )

#### **Constricted tracks**

- Generating the heat by current applying

- Measuring of the temperature

#### **Furthermore**

- Simulation of the power dissipated by the interconnection environment

- Assembly modification to maintain the  $\succ$ temperature (accurate  $\Delta T$ )

Figure 12: Experimental, analytical and simulated curves of the constriction track

life.augmented

Introduction

Context

Manufacturing process

**Experimental results**

Conclusion

MiNaPAD Forum 2019

# CONCLUSION

#### **Evolution of the power modules**

Power semiconductor devices integration is sought

### **Proposed approach**

- PCB-embedding technology

- Macro-nano structured interconnections

### **Best advantages**

- Flex interconnection

- Double side heat dissipation

- Low stray inductances

- Manufacturing process (common electronics product line and mass production)

### **Experimental results**

- Parallel electroplating and electro-etching validated

- > Low interconnection resistance approximatively 115  $\mu\Omega$ .cm<sup>-2</sup>

- Thermal resistance's measure in progress

# Thank you for your attention.

b.djuric@fr.merce.mee.com

This work is carried out as part of a partnership between Mitsubishi Electric R&D Centre Europe, Rennes and the Laplace laboratory of the University of Toulouse.

# **BIBLIOGRAPHY I**

Shur, Michael. (2019). Wide Band Gap Semiconductor Technology: State-of-the-Art. Solid-State Electronics. 10.1016/j.sse.2019.03.020.

N. Videau et al., "5-phase interleaved buck converter with gallium nitride transistors," The 1st IEEE Workshop on Wide Bandgap Power Devices and Applications, Columbus, OH, 2013, pp. 190-193.

M. Meisser, M. Schmenger and T. Blank, "Parasitics in Power Electronic Modules: How parasitic inductance influences switching and how it can be minimized," Proceedings of PCIM Europe 2015; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 2015, pp. 1-8.

B. Vidal, Paul-Etienne and Medjahed, Hassen and Nogarède, "Thermo-mechanical stress of bonded wires used in high power modules with Alternating and Direct Current modes," vol. 52, pp. 1099–1104, 2012.

*R. Gilardoni, "Ribbon Bonding for High Frequency Applications Advantages of Ribbon and the Impact on the Microwave Market."*

# **BIBLIOGRAPHY II**

J. G. Bai, J. N. Calata, and G.-Q. L. G.-Q. Lu, "Comparative thermal and thermomechanical analyses of solder-bump and direct-solder bonded power device packages having double-sided cooling capability," Ninet. Annu. IEEE Appl. Power Electron. Conf. Expo. 2004. APEC '04., vol. 2, no. C, pp. 1240–1246, 2004.

K. Siddabattula, Z. Chen, and D. Boroyevich, "Evaluation of Metal Post Interconnected Parallel Plate Structure for Power Electronic Building Blocks," 2000.

W. San, D. Risaletto, F. Richardeau, G. Blondel, M. Chemin, and P. Baudesson, "Microelectronics Reliability Preliminary failure-mode characterization of emerging directlead-bonding power module . Comparison with standard wire-bonding interconnection," vol. 55, pp. 1956–1960, 2015.

J. Xu, "Technology for Planar Power Semiconductor Devices Package with Improved Voltage Rating," 2008.

# **BIBLIOGRAPHY III**

Y. Zhao et al., "Silver sintering die attach process for IGBT power module production," 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, 2017, pp. 3091-3094.

L. Ménager, B. Allard, and V. Bley, "Conditionnement des modules de puissance."

W. D. Macdonald and T. W. Eagar, "TRANSIENT LIQUID PHASE BONDING PROCESSES Abstract."

E. Vagnon, J. Crebier, Y. Avenas, and P.-O. Jeannin, "Etudes de faisabilité d'un module de puissance 3D de type press- pack pour des applications de faible et moyenne puissances," Hal, 2008.

Y. Zhang, T. Hammam, I. Belov, T. Sjogren, M. Bakowski, and H.-P. Nee, "Thermomechanical Analysis and Characterization of a Press-Pack Structure for SiC Power Module Packaging Applications," IEEE Trans. Components, Packag. Manuf. Technol., vol. 7, no. 7, pp. 1089–1100, 2017.

# **BIBLIOGRAPHY IV**

M. Bassem, "Assemblages innovants en électronique de puissance utilisant la technique de Spark Plasma Sintering," 2013.

R. A. Beaupre, A. V. Gowda, L. D. Stevanovic, and S. A. Solovitz, "Double side cooled power module with power overlay," 2016.

B. C. Charboneau et al., "Double-sided liquid cooling for power semiconductor devices using embedded power packaging," in Fourtieth IAS Annual Meeting. Conference Record of the 2005 Industry Applications Conference, 2005.

Y. Tanaka, K. Ota, H. Miyano, Y. Shigenaga, T. Iizuka, and K. Tatsumi, "High Temperature Resistant Packaging for SiC Power Devices Using Interconnections Formed by Ni," no. 1, pp. 1371–1376, 2015.

G. Regnat and H. Id, "Onduleu a forte intégration utilisant des semi-conducteur a grand gap."

K. Mohan and N. Shahane, "Nanoporous Copper for Reliable, High-Temperature and High-Power Die-Attach Interconnections," pp. 3083–3090, 2017.

# **BIBLIOGRAPHY V**

Y. Pascal, D. Labrousse, M. Petit, S. Lefebvre, F. Costa, and C. National, "PCB - Embedding of Power Dies Using Pressed Metal Foam," no. June, pp. 5–7, 2018.

B. Mouawad et al., "3-Dimensional , Solder-Free Interconnect Technology for High-Performance Power Modules," vol. 9, pp. 1–6.

"Carbon Nanotubes Properties and Applications," Cheap Tubes Inc., 2018.

V. H. Nguyen et al., "Fabrication of bottom die substrate solderless interconnection based on nano copper wires Keywords Fabrication technique AAO template," pp. 1–9.